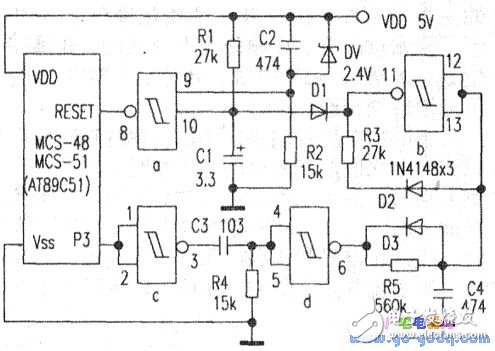

This circuit is designed for use in single-chip systems such as the MCS-51 series. The electrical schematic is illustrated in the diagram below.

In the figure, a four-input "2-NAND" Schmitt trigger 74HC132 is used. Gates C, D, B, along with components like C3, C4, R4, R5, D3, and D2, form the core of the circuit.

I-Beam Inductors,Chip Inductors,Color Ring Inductor,R-Bar Inductors

Shenzhen Sichuangge Magneto-electric Co. , Ltd , https://www.scginductor.com